| <u>_</u> | Simple schedule                                                                                                                                                                                                                                                                                                                         | <u>Schedule loads early</u>                |                                                                                |                                                                                                                                                                                                                                                                       |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Start    | Operations                                                                                                                                                                                                                                                                                                                              | Start                                      | Or                                                                             | perations                                                                                                                                                                                                                                                             |  |

| 13<br>15 | loadAI $r_{arp}.@a \Rightarrow r_1$<br>add $r_1.r_1 \Rightarrow r_1$<br>loadAI $r_{arp}.@b \Rightarrow r_2$<br>mult $r_1.r_2 \Rightarrow r_1$<br>loadAI $r_{arp}.@c \Rightarrow r_2$<br>mult $r_1.r_2 \Rightarrow r_1$<br>loadAI $r_{arp}.@d \Rightarrow r_2$<br>mult $r_1.r_2 \Rightarrow r_1$<br>storeAI $r_1 \Rightarrow r_{arp}.@a$ | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>9<br>11 | loadAI ra<br>loadAI ra<br>add r1<br>mult r1<br>loadAI ra<br>mult r1<br>mult r1 | $\begin{array}{c} rp, @a \Rightarrow r_1 \\ rp, @b \Rightarrow r_2 \\ rp, @c \Rightarrow r_3 \\ , r_1 \Rightarrow r_1 \\ , r_2 \Rightarrow r_1 \\ rp, @d \Rightarrow r_2 \\ , r_3 \Rightarrow r_1 \\ , r_2 \Rightarrow r_1 \\ , r_2 \Rightarrow r_{1r_3} \end{array}$ |  |

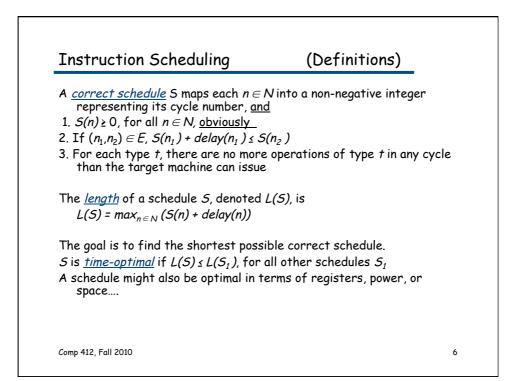

| ALU Characteristics                                                                      |                                 |      |  |  |  |  |

|------------------------------------------------------------------------------------------|---------------------------------|------|--|--|--|--|

| <ul><li>This data is surprisingly hard to mea</li><li>Value-dependent behavior</li></ul> | Intel E5530 operation latencies |      |  |  |  |  |

| <ul> <li>Context-dependent behavior</li> </ul>                                           | Instruction                     | Cost |  |  |  |  |

| <ul> <li>Compiler behavior</li> </ul>                                                    | 64 bit integer subtract         | 1    |  |  |  |  |

| <ul> <li>Have seen gcc underallocate &amp;</li> </ul>                                    | 64 bit integer multiply         | 3    |  |  |  |  |

| inflate operation costs with                                                             | 64 bit integer divide           | 41   |  |  |  |  |

| memory references (spills)                                                               | Double precision add            | 3    |  |  |  |  |

| <ul> <li>Have seen commercial compiler<br/>generate 3 extra ops per divide</li> </ul>    | Double precision subtract       | 3    |  |  |  |  |

| raising effective cost by 3                                                              | Double precision multiply       | 5    |  |  |  |  |

| • Difficult to reconcile measured                                                        | Double precision divide         | 22   |  |  |  |  |

| reality with the data in the                                                             | Single precision add            | 3    |  |  |  |  |

| Manuals (e.g. integer divide                                                             | Single precision subtract       | 3    |  |  |  |  |

| on Nehalem)                                                                              | Single precision multiply       | 4    |  |  |  |  |

|                                                                                          | Single precision divide         | 14   |  |  |  |  |

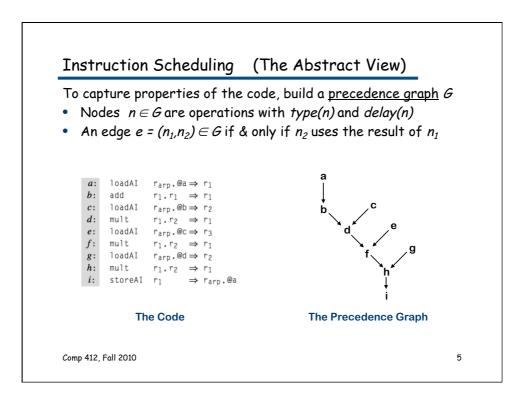

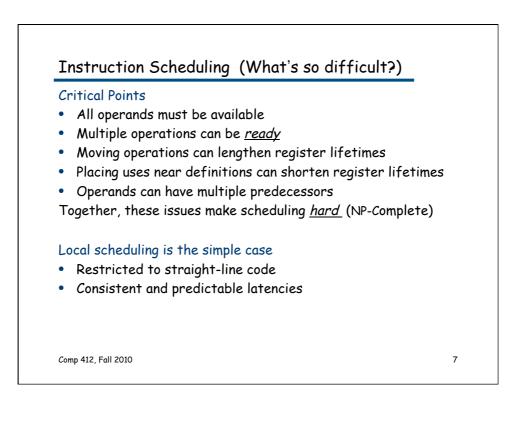

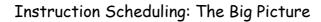

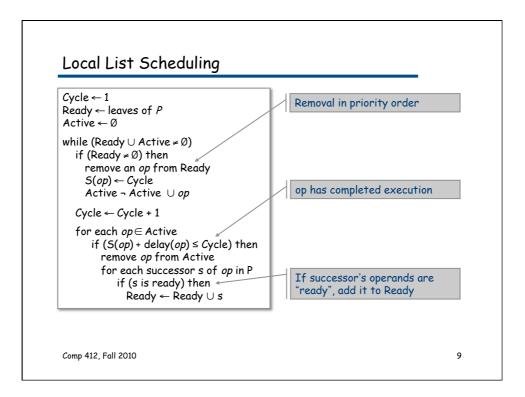

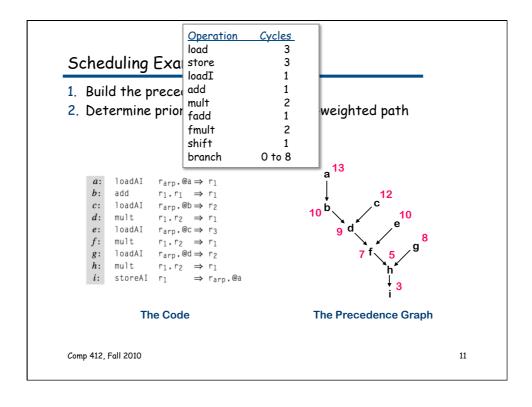

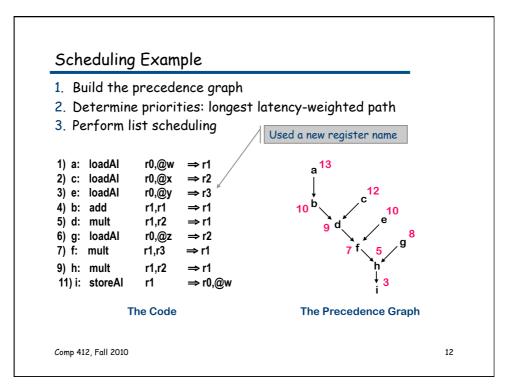

- 1. Build a precedence graph, P

- 2. Compute a *priority function* over the nodes in P

- 3. Use list scheduling to construct a schedule, 1 cycle at a time a. Use a queue of operations that are ready

- b. At each cycle

- I. Choose the highest priority ready operation & schedule it

\*8

II. Update the ready queue

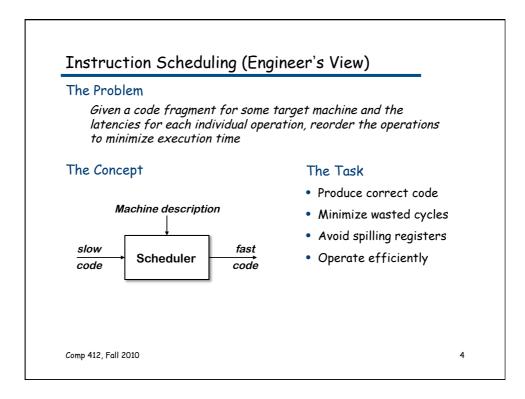

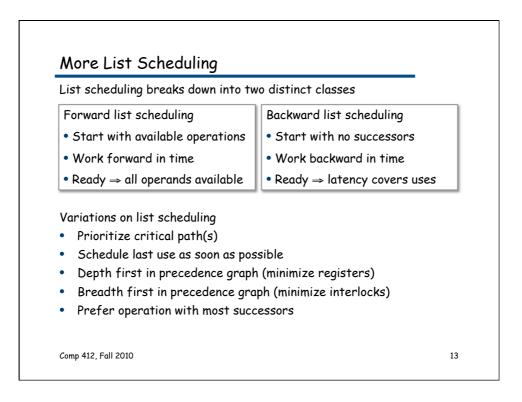

## Local list scheduling

- The dominant algorithm for thirty years

- A greedy, heuristic, local technique

Comp 412, Fall 2010

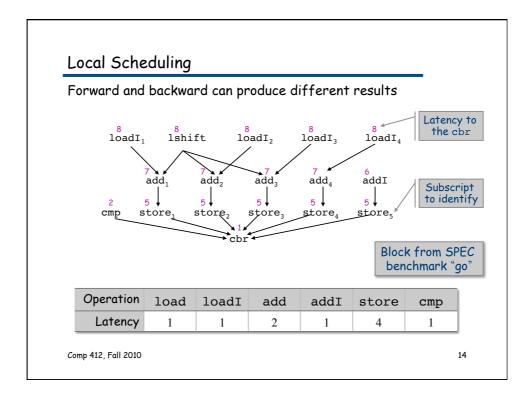

| 2 |    | Int                | Int                | Mem       | B      |    | Int              | Int                | Mem   |

|---|----|--------------------|--------------------|-----------|--------|----|------------------|--------------------|-------|

|   | 1  | loadI <sub>1</sub> | lshift             |           | ۵      | 1  | loadI4           |                    |       |

| / | 2  | loadI <sub>2</sub> | loadI <sub>3</sub> |           | c<br>k | 2  | addI             | lshift             |       |

|   | 3  | loadI <sub>4</sub> | $add_1$            |           | Ŵ      | 3  | $add_4$          | loadI <sub>3</sub> |       |

|   | 4  | $add_2$            | $add_3$            |           | ۵      | 4  | add <sub>3</sub> | loadI <sub>2</sub> | store |

|   | 5  | $add_4$            | addI               | $store_1$ | r<br>d | 5  | add <sub>2</sub> | $loadI_1$          | store |

|   | 6  | cmp                |                    | $store_2$ |        | 6  | $add_1$          |                    | store |

|   | 7  |                    |                    | $store_3$ | S      | 7  |                  |                    | store |

|   | 8  |                    |                    | $store_4$ | c<br>h | 8  |                  |                    | store |

|   | 9  |                    |                    | $store_5$ | e      | 9  |                  |                    |       |

|   | 10 |                    |                    |           | d      | 10 |                  |                    |       |

| 2 | 11 |                    |                    |           | u<br>I | 11 | cmp              |                    |       |

|   | 12 |                    |                    |           | e      | 12 | cbr              |                    |       |

|   | 13 | cbr                |                    |           |        |    |                  |                    |       |